# **OPERATOR'S MANUAL**

# MA1801/MA1801A

**Dual Waveform Generator**

Manual Revision 03/30/06 Manual Part Number: MAOM002 Instrument Part Number: MA1801/MA1801A Instrument Firmware 1.12

#### **CERTIFICATION**

Talon Instruments certifies that this product met its published specifications at the time of shipment from the factory.

#### WARRANTY

Talon Instruments products are warranted against defects in materials and workmanship as follows:

- (a) One year for the MA1801/MA1801A.

- (b) Ninety days for cables.

During the warranty period, Talon Instruments will, at its option, either repair or replace products which prove to be defective.

For warranty service or repair, this product must be returned to the Talon Instruments factory. Buyer shall prepay shipping charges to the factory and Talon Instruments shall pay shipping charges to return the product to the Buyer. However, Buyer shall pay all shipping charges, duties, and taxes for products returned to Talon Instruments from another country.

Talon Instruments warrants that its software and firmware designated by Talon for use with its instruments will execute its programming instructions when properly installed on the instrument. Talon Instruments does not warrant that the operation of the instrument, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The foregoing warranty shall not apply to defects resulting from improper or inadequate maintenance by the Buyer, Buyer-supplied software or interfacing, unauthorized modification or misuse, operation outside of environmental specifications for the product, or improper site preparation or maintenance.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED. TALON INSTRUMENTS SPECIFICALLY DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **EXCLUSIVE REMEDIES**

THE REMEDIES PROVIDED HEREIN ARE BUYER'S SOLE AND EXCLUSIVE REMEDIES. TALON INSTRUMENTS SHALL NOT BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, WHETHER BASED ON CONTRACT, TORT, OR ANY OTHER LEGAL THEORY.

# **SAFETY FIRST**

# PROTECT YOURSELF AND THE EQUIPMENT. Follow these precautions:

- Don't repair the module unless you are a qualified electronics technician and have instructions from Talon Instruments.

- Pay attention to the WARNING statements. They point out situations that can cause injury or death.

- Pay attention to the CAUTION statements. They point out situations that can cause equipment damage.

- Use ESD static control procedures when handling the MA1801/MA1801A or any of its modules.

# **Table of Contents**

| 1 | Introduction                                   | 1-1 |

|---|------------------------------------------------|-----|

|   | 1.1 General                                    | 1-1 |

|   | 1.2 Specifications                             | 1-1 |

|   | 1.2.1 Module                                   | 1-1 |

|   | 1.2.2 Environmental                            |     |

|   | 1.2.3 Size                                     |     |

|   | 1.2.4 Power                                    |     |

|   | 1.2.6 Bus Compliance                           |     |

| 2 | Preparation                                    |     |

| _ | 2.1 Receiving Inspection                       |     |

|   | 2.1.1 Unpacking Instructions                   |     |

|   | 2.1.2 Handling Precautions                     |     |

|   | 2.1.3 Returning Equipment                      |     |

|   | 2.1.4 Storage                                  |     |

|   | 2.2 Hardware Installation                      | 2-2 |

|   | 2.2.1 Master/Slave Cable                       | 2-2 |

|   | 2.3 Software Installation                      | 2-3 |

|   | 2.3.1 VXI Plug&Play Instrument Driver          | 2-3 |

| 3 | Functional Description                         | 3-1 |

|   | 3.1 Hardware Block Diagrams                    | 3-1 |

|   | 3.1.1 Basic Block Diagram                      | 3-1 |

|   | 3.1.1.1 Variable Voltage Inputs                | 3-1 |

|   | 3.1.1.2 Channel A and Channel B                | 3-2 |

|   | 3.1.1.3 16 - Bit Timer                         | 3-2 |

|   | 3.1.1.4 TRIGA/TRIGB Outputs                    | 3-2 |

|   | 3.1.1.5 Inter-Module Interface                 | 3-2 |

|   | 3.1.2 Channel Block Diagram                    | 3-2 |

|   | 3.1.2.1 Primary and Secondary Memory           | 3-3 |

|   | 3.1.2.2 Sequence Control                       | 3-3 |

|   | 3.1.2.3 Clock Generator                        | 3-3 |

|   | 3.1.2.4 Sample Clock Divider                   | 3-3 |

|   | 3.1.2.5 Sweep Divide Memory                    | 3-3 |

|   | 3.1.2.6 Sequencer                              | 3-4 |

|   | 3.1.2.7 14 - Bit D/A                           | 3-4 |

|   | 3.1.2.8 Filter                                 | 3-5 |

|   | 3.1.2.9 Relay                                  | 3-5 |

|   | 3.1.2.10 SIGOUT1/SIGOUT2 Outputs               | 3-5 |

|   | 3.2 Module Connectors                          | 3-5 |

|   | 3.2.1 M/MA-Module Logic Bus Connector (PCB-J9) |     |

|   | 3.2.2 Inter Module Connector (PCB-J8)          |     |

|   | 3.2.3 FPGA Program Connector (PCB-J1)          |     |

|   | 0.2.7 Oddia Odilicotolo (1 lolit 1 dictivion)  | J-U |

|   | 3.2.5 I/O Connector (Front Panel J1)                  | . 3-5  |

|---|-------------------------------------------------------|--------|

|   | 3.3 Identification/Configuration Registers            | 3-6    |

|   | 3.3.1 M-Module PROM Registers                         | 3-6    |

|   | 3.3.2 IO Registers                                    | . 3-7  |

| 4 | Register Operation.                                   |        |

|   | 4.1 Initialize Clock/DAC Registers                    |        |

|   | 4.2 Check the MA1801A Arm Status                      |        |

|   | 4.3 Stopping a Channel                                |        |

|   | 4.4 Setting the Amplitude/Offset                      | . 4-3  |

|   | 4.5 Setting the Sample Clock                          |        |

|   | 4.6 Programming the Waveform Memory                   |        |

|   | 4.7 Programming the Sequence Memory                   |        |

|   | 4.8 Setting the Internal Timer Period                 |        |

|   | 4.9 Setting the Operating Mode                        | . 4-11 |

|   | 4.10 Arming the Channel                               |        |

|   | 4.11 Generating Manual Triggers                       |        |

|   | 4.12 Assigning Stop/Restart Signals                   |        |

|   | 4.13 Setting the Output Signal Source                 |        |

|   | 4.14 Programming Sync Pulse/Replace                   |        |

|   | 4.15 Setting Channel Coupling                         |        |

|   | 4.16 Setting Sample Clock Divider                     |        |

|   | 4.17 Setting Start Trigger Delay                      |        |

|   | 4.18 Setting Input Thresholds                         |        |

|   | 4.19 Generating Status/Event Interrupts               |        |

|   | 4.19.1 Status Register.                               |        |

|   | 4.19.2 Event Register                                 |        |

|   | 4.19.3 Event Enable (Interrupts)                      |        |

|   | 4.20 Setting Trigger Timeout                          |        |

| 5 | Register Operation Examples                           |        |

| 0 | 5.1 Example 1: Single Waveform Triggered              |        |

|   | 5.1.1 Example 1 Main                                  |        |

|   | 5.1.2 Example 1 Waveform                              |        |

|   | 5.1.3 Example 1 Burst Mode Exercise                   |        |

|   | 5.2 Example 2: Multiple Waveforms with Manual Trigger |        |

|   | 5.2.1 Example 2 Main                                  | . 5-4  |

|   | 5.2.2 Example 2 Waveform                              |        |

|   | 5.3 Example 3: Continuous Waveform with Stop/Start    | 5-5    |

|   | 5.3.1 Example 3 Main                                  | 5-5    |

|   | 5.3.2 Example 3 Waveform                              | 5-6    |

|   | 5.4 Example 4: Sync Pulse Output                      | 5-6    |

|   | 5.4.1 Example 4 Main                                  | 5-6    |

|   | 5.4.2 Example 4 Waveform                              |        |

|   | 5.4.3 Example 4 Sync Replace Exercise                 |        |

|   | 5.5 Example 5: Multi Channel Waveform                 |        |

|   | 5.5.1 Example 5 Main                                  | 5-9    |

|     | 5.5.2        | Example 5 Waveform                    | . 5-10 |

|-----|--------------|---------------------------------------|--------|

| 5.6 | Exa          | mple 6 Channel Coupling               | . 5-10 |

|     | 561          | Example 6 Main                        | 5-10   |

|     |              | Example 6 Waveform                    |        |

|     |              | Example 6 Clock Divider Exercise      |        |

|     |              | Example 6 Trigger Delay Exercise.     |        |

|     |              | MA1801A Register Map                  |        |

|     |              |                                       |        |

| 1   |              | duction                               |        |

| 2   | I/O N        | Memory                                | . A-1  |

|     | 2.1          | Memory/Run Control (0h)               | . A-1  |

|     | 2.2          | Start Delay (4h)                      |        |

|     | 2.3          | Start/Output Control (8h)             | . A-3  |

|     | 2.4          | Timeout Control (Ch)                  |        |

|     | 2.5          | Stop/Restart Control (10h)            | . A-5  |

|     | 2.6          | Sync A Control 1 (14h)                |        |

|     | 2.7          | Sync A Control 2 (18h)                | . A-6  |

|     | 2.8          | Sync A Control 3 (1Ch)                | . A-7  |

|     | 2.9          | Sync B Control 1 (20h)                |        |

|     | 2.10         | Sync B Control 2 (24h)                | . A-7  |

|     | 2.11         | Sync B Control 3 (28h)                | . A-8  |

|     | 2.12         | Sequence Control 1 (2Ch)              |        |

|     | 2.13         | Sequence Control 2 (30h)              |        |

|     | 2.14         | Signal/Clock Control (34h)            |        |

|     | 2.15         | Interval Timer (38h)                  |        |

|     | 2.16         | First Sequence (3Ch)                  |        |

|     | 2.17         | Clock Generator Control 1 (40h)       |        |

|     | 2.18         | Clock Generator Control 2 (44h)       |        |

|     | 2.19         | Clock Generator Control 3 (48h)       |        |

|     | 2.20         | Gain Channel A (80h)                  |        |

|     | 2.21         | Gain Channel B (84h)                  |        |

|     | 2.22         | Offset Channel A (88h)                |        |

|     | 2.23         | Offset Channel B (8Ch)                |        |

|     | 2.24         | Trigger1A Reference Level (90h)       |        |

|     | 2.25         | Trigger1B Reference Level (94h)       |        |

|     | 2.26         | Reference Clock Reference Level (98h) |        |

|     | 2.27         | External Clock Reference Level (9Ch)  |        |

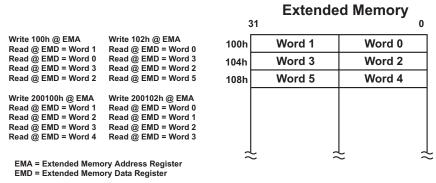

|     | 2.28         | Extended Memory Address / Page (C0h)  |        |

|     | 2.29         | Extended Memory Data (C4h)            |        |

|     | 2.30         | Sample Clock Divider A (C8h)          |        |

|     | 2.31         | Sample Clock Divider B (CCh)          |        |

|     | 2.32         | Status A (D0h)                        |        |

|     | 2.33<br>2.34 | Event A (D4h)                         |        |

|     | 2.35         | Event Enable A (D8h)                  |        |

|     | 2.36         | ,                                     |        |

|     | 2.36         | Status B (E0h)                        |        |

|     | 2.38         | Event Enable B (E8h).                 |        |

|     | 2.30         | Address Readback B (ECh)              |        |

|     | 2.40         |                                       |        |

|     | 2.40         | Sweep Register A (F0h)                |        |

|     | 2.41         | MA1801A Version/IDPROM (FCh).         |        |

|     |              | · · ·                                 |        |

| 3   | ⊨xte         | ended Memory                          | . A-21 |

| 3.1        | Waveform Memory               | . A-21 |

|------------|-------------------------------|--------|

| 3.2        | Sequence Memory               | A-22   |

| 3.3        | Persistence Memory            | A-23   |

| 3.4        | Sweep Frequency Divide Memory | A-23   |

| Appendix B | Signal Description            | B-1    |

| 1 MC>      | Coaxial Connectors            | B-1    |

| 2 J1 C     | onnector                      | B-1    |

| Appendix C | Example Code                  | C-1    |

# **List of Tables**

| Table 3-1 M/MA Module EEPROM IDENT Words | . 3-6 |

|------------------------------------------|-------|

| Table A-1 I/O Memory Register Map        | . A-1 |

# 1 Introduction

#### 1.1 General

The Model MA1801/MA1801A, hereafter referred to as MA1801A, is a single slot MA-Module that contains two 14-bit arbitrary waveform generator channels which can operate independently or in lock step. The maximum sample rate is 125 MS/s. All waveforms are output from data loaded into waveform memory.

Waveform memory (1M samples/channel) is provided so that multiple waveforms can be loaded at once. Also, memory paging allows one page of memory to be outputting while the other page is being re-loaded with new data.

Powerful sequencing allows waveform segments to be looped and output in any order. There are also provisions for jumping to different sequences based on a trigger input (with or without return).

Flexible triggering is also provided to start/stop/restart the waveform or for advancing to the next segment.

A sync pulse can be placed anywhere in the waveform. It also can be of varying width. During the sync pulse, an alternate waveform can replace the waveform currently being output.

Up to 4 adjacent MA1801A modules can be linked together (in a VXI carrier, for example) to provide 8 ARB channel outputs which are running synchronously.

# 1.2 Specifications

| 2.1  | Module                                                  |                     |

|------|---------------------------------------------------------|---------------------|

|      | ARB Channels                                            | 2                   |

|      | Memory per Channel                                      |                     |

|      | Banks (Primary/Secondary)                               | 2                   |

|      | Size                                                    |                     |

|      | Signal Outputs (SigOut1A, SigOut2A, SigOut1B, SigOut2B) | 4                   |

|      | Configuration                                           |                     |

|      | Driver                                                  |                     |

|      | Current                                                 |                     |

|      | Termination                                             |                     |

|      | Signal Source                                           |                     |

|      | Trigger/Advance Inputs                                  | Ookware Gelectable  |

|      | Front Panel Analog (TRIG1A, TRIG2A)                     | 2                   |

|      | Front Panel TTL (TRIG2A, TRIG2B)                        | 2                   |

|      | M-Module Bus (TRIGA, TRIGB)                             |                     |

|      | Internal Timer (TIMERA, TIMERB)                         |                     |

|      | Sequence Flag                                           |                     |

|      | Arb Marker                                              |                     |

|      | Trigger/Advance Signal Control                          | Software Selectable |

|      | Active High, Active Low, Rising Edge, Falling Edge      |                     |

|      | Trigger Range                                           | DC to 20MHz         |

|      | Trigger Delay                                           |                     |

|      | Trigger Response Delay                                  |                     |

|      | Amplitude Modulation Input                              |                     |

|      | Master Clock Input                                      |                     |

|      | Master Clock Reference Input                            | 1                   |

| Fr   | ont Panel Analog Inputs (TRIG1A, TRIG1B)                |                     |

|      | Configuration                                           | Single Ended        |

|      | Connector                                               |                     |

|      | Impedance                                               |                     |

|      | Range                                                   |                     |

|      | Threshold                                               |                     |

|      | Resolution                                              | 5mV (12 bits)       |

|      | Accuracy                                                | 100mÚ               |

| Fr   | ont Panel TTL Inputs (TRIG2A, TRIG2B)                   |                     |

|      | Configuration                                           | Single Ended        |

|      | Connector                                               |                     |

|      | Receiver                                                |                     |

|      | Impedance                                               |                     |

| Δr   | nplitude Modulation Input                               | 10100               |

| . (1 | •                                                       | BAOV (ABA)          |

|      | Connector                                               |                     |

|      | Impedance                                               | 10KΩ , ±5%          |

|      |                                                         |                     |

|                                                                                                                                                                                                                                                                                        | ~2V pk-pk for 90% modulation           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| alog Outputs (1 per channel)                                                                                                                                                                                                                                                           |                                        |

| Configuration                                                                                                                                                                                                                                                                          | Single end                             |

| Connector                                                                                                                                                                                                                                                                              | Front panel MCX (OA, O                 |

| Stand-by                                                                                                                                                                                                                                                                               | Normal or output off (relay disconne   |

| Impedance                                                                                                                                                                                                                                                                              | 50Ω, ±1                                |

| Short-circuit Protection                                                                                                                                                                                                                                                               | Any voltage between ±1:                |

| Output Range                                                                                                                                                                                                                                                                           | , -                                    |

|                                                                                                                                                                                                                                                                                        | ±1                                     |

|                                                                                                                                                                                                                                                                                        | ±                                      |

| Gain control                                                                                                                                                                                                                                                                           |                                        |

|                                                                                                                                                                                                                                                                                        | 12 b                                   |

|                                                                                                                                                                                                                                                                                        | 1% of programmed value $\pm$ 50r       |

| Accuracy MA1801A                                                                                                                                                                                                                                                                       | ± 50r                                  |

| Offset                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                                                                                                                                                                                                        | ±1                                     |

|                                                                                                                                                                                                                                                                                        | ±                                      |

|                                                                                                                                                                                                                                                                                        | 5 mV (12-bits): 1.25mV in increment mo |

|                                                                                                                                                                                                                                                                                        | 1% of programmed value $\pm$ 50 ه      |

|                                                                                                                                                                                                                                                                                        | ± 50 ı                                 |

| Filter                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                                                                                                                                                                                                        | on/                                    |

|                                                                                                                                                                                                                                                                                        | 7-pole ellip                           |

| Fco                                                                                                                                                                                                                                                                                    | 50 M                                   |

| ernal Timers                                                                                                                                                                                                                                                                           |                                        |

| ······                                                                                                                                                                                                                                                                                 |                                        |

|                                                                                                                                                                                                                                                                                        | 20 μsec to 1.3107 s                    |

|                                                                                                                                                                                                                                                                                        |                                        |

| Range                                                                                                                                                                                                                                                                                  |                                        |

| Range<br>Resolution                                                                                                                                                                                                                                                                    |                                        |

| Range Resolution uster Clock Internal                                                                                                                                                                                                                                                  |                                        |

| Range Resolution uster Clock Internal Range                                                                                                                                                                                                                                            | 20 μs                                  |

| Range Resolution  Ister Clock  Internal Range Resolution                                                                                                                                                                                                                               |                                        |

| Range Resolution  ster Clock  Internal Range Resolution Accuracy Jitter                                                                                                                                                                                                                |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference                                                                                                                                                                                                   |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector                                                                                                                                                                                         |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance                                                                                                                                                                               |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Range                                                                                                                                                                   |                                        |

| Range Resolution  ster Clock  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Range Feed through                                                                                                                                          |                                        |

| Range Resolution  ster Clock  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold                                                                                                                                      |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution                                                                                                                                       |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy.                                                                                                                             |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy Jitter External                                                                                                              |                                        |

| Range Resolution  ster Clock  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy External Connector                                                                                               |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy.  External Connector Frequency                                                                                               |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy.  External Connector Frequency Edge rate                                                                                     |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy  External Connector Frequency Edge rate Impedance Impedance                                                                  |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy External Connector Frequency Edge rate Impedance Range Range Range Range Resolution Accuracy                                 |                                        |

| Range Resolution  Internal Range Resolution Accuracy Jitter External 10MHz Reference Connector Impedance Range Feed through Threshold Resolution Accuracy  External Connector External Connector Frequency Edge rate Impedance Range Range Facel through Threshold Resolution Accuracy |                                        |

#### Sample Clock

Divided down from the master clock using a 1-32 bit binary divider.

#### **Linked Operation**

Channel B may be Linked to Channel A on the MA1801A. In Linked operation, Channel A provides the Sample Clock, Triggers and Gates to Channel B so that the two MA1801A modules will be running in lock step.

#### Master/Slave Operation

Up to 4 adjacent MA1801A Modules can be linked together on a single carrier using an available inter-module cable. Channel A on one module is designated as the Master. Any of the other channels can be slaves or operated independently.

ently.

The Master channel provides the Sample Clock, Triggers and Gates to the designated Slave channels so that they will all be running in lock step with the master Channel.

#### **Software**

The MA1801A is provided with VISA Plug&Play Instruments Driver and a Soft Front Panel.

#### 1.2.2 Environmental

#### **Temperature Range**

|       | Storage:                               | 40°C to +71°C (RH not controlled.)                                               |

|-------|----------------------------------------|----------------------------------------------------------------------------------|

| Al    | titude:                                |                                                                                  |

|       | 0°C to +10<br>+11°C to +<br>+31°C to + | Sea level to 10,000 ft. Sea level to 15,000 ft. Umidity (non-condensing)  °C:    |

| 1.2.3 | Size                                   |                                                                                  |

|       | Dimension:<br>Weight:                  | s:Single-wide MA-Module. 5.687"(144.5mm) long X 2.082"(52.9mm)<0.113 kg (4 oz.). |

#### 1.2.4 **Power**

Total: < 10 Watts

| Voltage | Peak Current | Dynamic Current |

|---------|--------------|-----------------|

| +5 Vdc  | 1.2 A        | TBD             |

| +12 Vdc | 0.2 A        | TBD             |

| -12 Vdc | 0.3 A        | TBD             |

### 1.2.5 Cooling Requirements

For 10° C degree rise TBD I/s, TBD mm H20

### 1.2.6 Bus Compliance

The MA1801A module complies with the ANSI/VITA 12-1996 Specification for double wide M-Modules and the MA-Module trigger signal extension. The module also supports the optional IDENT and VXI-IDENT functions.

Module Type: MA-Module

Addressing: A08/A24

Data: D16/D32

Interrupts INTA & INTC

DMA not supported

Triggers: TRIGA and TRIGB

Identification IDENT and VXI-IDENT

Manufacturer ID F0F16

Model Number 00CC16

VXI Model Code 070916

Revision Level 000116

# 2 Preparation

# 2.1 Receiving Inspection

Check the shipment at the time of delivery and inspect each box for damage. Describe any box damage and list any shortages on the delivery invoice.

#### 2.1.1 Unpacking Instructions

- 1. Unpack the box in a clean and dry environment. Save all the packing material in case the instrument must be returned for repair. The following is the packing list of the MA1801A.

- A. MA1801A MA-Module

- B. MA1801/MA1801A Operators Manual

- C. Front Panel J1 Mating Connector

- D. Mounting hardware (4-M3x6mm slotted fillister head screws)

- E. System Software CD

- 2. Verify that all the items on the packing list have been included. Call Talon's Customer Service representative (800-722-2528) if any items are missing.

- 3. Inspect the equipment carefully for any signs of mechanical damage regardless of the condition of the shipping boxes.

- 4. In the case of mechanical damage, call the shipper immediately and start the claim process.

- 5. Call Talon's Customer Service representative (800-722-2528) to inform them that the shipment arrived damaged. Please be prepared to provide a detailed damage report.

#### 2.1.2 Handling Precautions

The MA1801A contains components that are sensitive to electrostatic discharge. When handling the module for any reason, do so at a static-controlled workstation, whenever possible. At a minimum, avoid work areas that are potential static sources, such as carpeted areas. Avoid unnecessary contact with the components on the module.

#### 2.1.3 Returning Equipment

Follow these steps when you return equipment to Talon:

- 1. Call Talon Instruments (800-722-2528) for a Return Material Authorization number (RMA). The Talon Customer Service representative will ask for your name, telephone number, company name, equipment type, model number, serial number, and a description of your problem.

- 2. If at all possible, always use the original shipping container. Use a double-walled cardboard shipping container. Protect all sides, including the top and bottom, with shock absorbing material (minimum of 1 inch thick material) to prevent movement of the MA1801A within the container. Seal the shipping container with approved sealing tape. Mark "FRAGILE" on all sides, top, and bottom of the shipping container. If you use inadequate material, you'll be responsible for any shipping damage repair as carriers won't accept responsibility on incorrectly packed equipment.

- 3. Pack and ship the equipment to:

Talon Instruments 4 Goodyear Irvine, CA 92618

Include the RMA number on the address label as well as the packing list.

#### 2.1.4 Storage

The MA1801A should be stored in a clean, dry environment. In high humidity environments, protect the MA1801A from temperature variations that could cause internal condensation. The following environmental conditions apply to both shipping and storage:

Temperature -40°C to +71°C

Relative Humidity not controlled, non-condensing

Altitude <40000 ft. (12192 m)

Vibration <2g Shock <40g

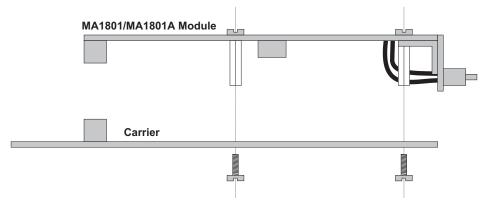

#### 2.2 Hardware Installation

All MA1801A modules must be installed into the carrier before the carrier is installed into the host system. MA1801A modules are installed by firmly pressing the connector on the MA1801A together with the connector on the carrier. Secure the MA1801A with mounting hardware provided as shown in figure 2-1.

Figure 2-1 MA1801A Installation

#### 2.2.1 Master/Slave Cable

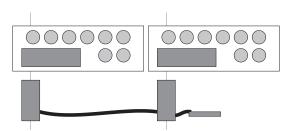

If multiple MA1801A modules are installed and the application requires coupling channels on different modules then the master/slave cable must be installed prior to installing the MA1801As on the carrier.

The master/slave cable, figure 2-2, is a daisy chain cable that routes the signals necessary for intermodule coupling and includes a termination block on the far right hand side.

Figure 2-2 Master/Slave Cable (Part Number MA/304)

Remove unused connectors and cable from the left hand side of the master/slave cable. Install the master/slave cable into the J8 connector on each MA1801A, figure 2-3. Install the group of MA1801As onto the carrier board.

Figure 2-3 Master/Slave Cable Installation

#### **CAUTION**

Make sure to connect the master/slave cable into the J8 connector and not the J1 connector on the MA1801A.

#### 2.3 Software Installation

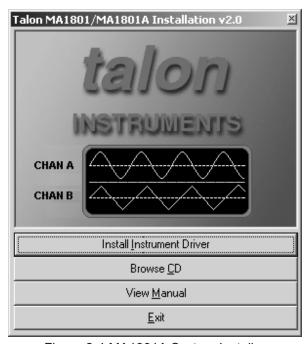

The MA1801A is shipped with a VXI Plug&Play Instrument Driver. The software is included on the CD shipped with the MA1801A system. In addition to the software, the CD also contains the operators manual for the MA1801A in PDF format.

#### 2.3.1 VXI Plug&Play Instrument Driver

The MA1801A Instrument Driver links the communication interface and an application development environment. It provides a higher level, more abstract view of the instrument. It also provides ADE-specific information that supports the capabilities of the ADE, such as a graphical representation. Some of the ADE that this Instrument Drivers supports are listed below:

- Borland Turbo C/C++

- Agilent Technologies Agilent VEE

- · Microsoft Visual Basic

- Microsoft Visual C/C++

- National Instruments LabVIEW

- National Instruments LabWindows/CVI

Included with the Instrument Driver is the Soft Front Panel. The soft front panel is a graphical user interface for the MA1801A. It is used to verify communications and functionality when the MA1801A is first integrated into the system.

The MA1801A VXI Plug&Play Instrument Driver requires that VISA be installed. Contact your Slot 0 Resource Manager manufacturer.

To install MA1801A Plug&Play Instrument Driver:

1. Insert the MA1801A System CD into your computer's CD-ROM drive. The MA1801A System Installation menu will run automatically. If the installation menu, figure 2-4, does not appear, run FastMenu.exe from the FastMenu directory on the CD.

Figure 2-4 MA1801A System Installer

- 2. Press the "Install Instrument Driver" command button.

- 3. The installer will remove any versions that are currently loaded on the computer.

- 4. If a previous version was removed in step 3, then repeat step 2.

- 5. Follow the installer directions.

- 6. After the Instrument Driver is installed, the MA1801A Soft Front Panel will be launched.

The following files are installed from the CD:

- ANSI C source code for the Instrument Driver and Soft Front Panel, i.e., .c and .h files.

- MS Windows 32 bit DLL library, i.e., tama1801\_32.dll and tama1801.def files.

- Microsoft 32 bit DLL import library, i.e., tama1801.lib file.

- Function panel file, i.e., tama1801.fp file.

- MS Visual Basic Function Declaration text file, i.e., tama1801.bas file.

- Windows help file, i.e., tama1801.hlp file.

Visit the Talon Instruments web site at "www.taloninst.com" and check for MA1801A Instrument Driver updates.

# **3 Functional Description**

This section describes the MA1801A hardware block diagram, module connectors and identification/configuration registers. The full address map is provided in appendix A of this manual.

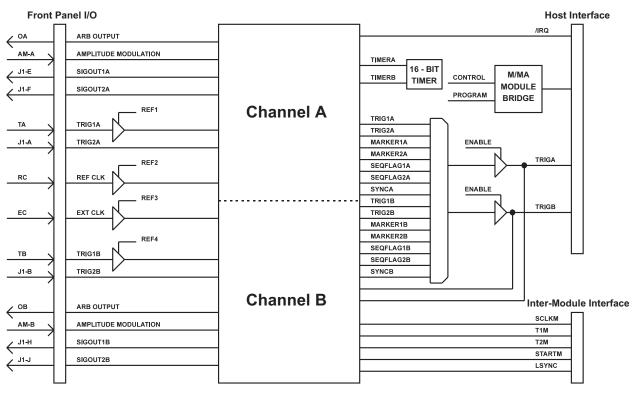

### 3.1 Hardware Block Diagrams

The MA1801A is a two channel arbitrary waveform generator. The MA1801A can output sample points at a rate up to 125M samples per second. Up to 1M sample points can be stored in static memory. Static memory is configured as two independent banks (primary and secondary) to allow dynamic update of the waveform memory. An intelligent sequencer and extensive triggering selections control the waveform memory to allow the user to create complex waveforms that includes looping, conditional branching and subroutines. The two channels can output independently or linked, in addition multiple MA1801As can be configured in a master/slave mode to provide more than two synchronized outputs.

#### 3.1.1 Basic Block Diagram

Figure 3-1 illustrates the basic block diagram of the MA1801A.

Figure 3-1 MA1801A Basic Block Diagram

#### 3.1.1.1 Variable Voltage Inputs

The MA1801A has four variable voltage inputs, TRIG1A, TRIG1B, EXT CLK and CLK REF.

TRIG1A and TRIG1B can be used to trigger a start, stop, restart or advance for either channel of the MA1801A.

The EXT CLK can be selected as the sample clock for either channel.

The REF CLK can be used as the internal clock generator reference for either channel. The REF CLK input must be 10MHz.

#### 3.1.1.2 Channel A and Channel B

Channel A and Channel B block diagrams are described in section 3.1.2.

#### 3.1.1.3 16 - Bit Timer

The 16 - Bit counter allows the user to program two timers, TIMERA and TIMERB. TIMERA and TIMERB can be used as the start, stop, restart, advance or jump signal for either channel of the MA1801A.

#### **NOTE**

In revision 1.12 the timers are reset at the beginning of a sequence when selected as the stop signal or at the beginning of each sequence step if specified as an advance or jump signal. In revision 1.11 TIMERA is rest when channel A is started and TIMERB is reset when channel B is started.

#### 3.1.1.4 TRIGA/TRIGB Outputs

The M-Module signals, TRIGA and TRIGB, can be programmed to output one of a number of signals for triggering other devices. TRIGA and TRIGB can be separately enabled.

#### 3.1.1.5 Inter-Module Interface

The inter-module interface connects adjacent MA1801A modules together in a master/slave configuration. One channel is designated as the master and broadcasts the clock, trigger, start and sync signals to the designated slaves.

#### 3.1.2 Channel Block Diagram

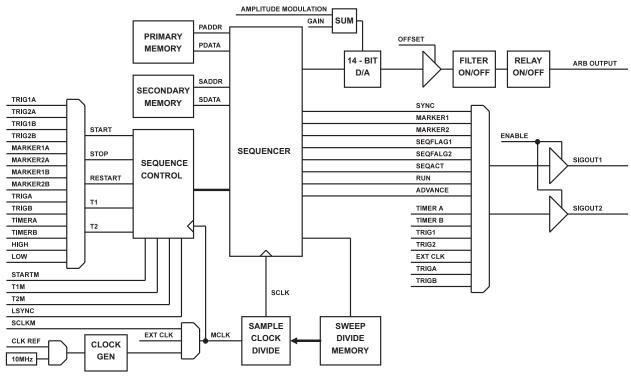

Figure 3-2 illustrates the channel block diagram for each channel.

Figure 3-2 Channel Block Diagram

#### 3.1.2.1 Primary and Secondary Memory

The primary and secondary memories contain the waveform data. Each memory is 32 bits by 256K. Each 32 bit memory location contains two waveform sample points. The waveform is formed by programming the sample points in these memories. While one bank is outputting waveform data the other bank can be programmed in a "ping-pong" fashion to output continually changing waveforms.

#### 3.1.2.2 Sequence Control

The sequence control allows the user to program how the sequencer starts/stops and advances from one sequence step to another.

The START, STOP and RESTART signals control when the sequencer is active as described below:

START The START signal is used to activate the sequencer and output the speci-

fied waveform. The START signal can only activate the sequence if the

channel has been armed.

STOP The STOP signal deactivates an active sequence waveform.

RESTART The RESTART signal reactivates a previously stopped sequence wave-

form.

The T1 and T2 signals control when the sequencer advances from one step to another.

The user can select the source of the five control signals described above. In addition the user can program the active state of the control signal from one of the following selections:

- Active High

- Active Low

- Rising Edge

- Falling Edge

The master/slave and linked mode selections determine which set of signals are used to control the sequencer, the local set or the external set from the inter-module interface. If Channel A is programmed as the master channel then the inter-module signals are driven by channel A.

Manual control of the start, stop, restart and advance functions can be performed through register access.

The system delay of the sequence control signals is 7 master clocks plus 20ns. See the frequency divider section 3.1.2.4 for steps to minimize the system delay.

#### 3.1.2.3 Clock Generator

An internal clock generator can be used to specify the sample clock. Every rising edge of the sample clock outputs a new waveform sample point.

The internal clock generator can be programmed from 1Hz to 125MHz.

The clock generators 10MHz reference clock can set to internal or external.

#### 3.1.2.4 Sample Clock Divider

The sample clock divider is a binary clock divider which is used for setting the sample clock (SCLK) rate. The divider is a 32 bit value that is programmed one less than the desired divide value (SCDIV). The formula for sample rate is:

```

SCLK = MCLK ÷ SCDIV

```

For minimal system delay, master clock (MCLK) should be set as high as possible with the sample clock divider then used to set the desired sample clock rate.

#### 3.1.2.5 Sweep Divide Memory

In sweep operations, the sample clock divider can be updated on the fly. An array of 256 divide values can be stored and cycled through for sweeping a waveform.

#### 3.1.2.6 Sequencer

The sequencer is a bank of static RAM that defines 512 separate sequence steps. Each sequence step identifies a block of waveform memory to output (called a segment).

A sequence can be defined to output one or more segments. The desired number of words for each segment step can be specified (i.e. all of a given segment or some portion of it). Each segment can be looped and a jump sequence can be defined (i.e. the sequence that will be executed next if the jump condition is met). A return flag can also be set (i.e. jump with return). A jump can also occur immediately or at the end of the present segment. When a jump with return occurs, the sequence step jumped to will be output in SING mode with auto advance and then return to the step that was jumped from.

Each sequence step can be looped up to 64k times.

Two Sequence Flags can be programmed. Each one can be set HI or LOW on each sequence step.

The mode which controls advancing from one sequence step to the next can be of one of the following choices:

STEP The sequence is advanced to the next step only when a valid trigger is received. The output of the MA1801A generates the current segment con-

tinuously until a trigger signal advances the sequence to the next step. If

loops were specified, they are ignored in STEP mode.

SING The MA1801A idles between steps until a valid trigger signal is sensed.

After outputting the specified number of loops, the output level idles at a DC level equal to the last point of the waveform. The sequencer will step to the next step in the sequence when it receives its next valid trigger.

SING1 The MA1801A idles between steps until a valid trigger signal is sensed.

After a trigger, the generator outputs one waveform loop. Then, the output level idles at a DC level equal to the last point of the last generated waveform. If loops were programmed, the sequencer repeats this segment each time a trigger is received, until the number of loops specified for this step has been reached. After reaching this number, the sequencer ad-

vances to the next step in the sequence.

A SYNC pulse can be defined to occur at any point during the output of the waveform. The reference starting point can be any one of the following:

- The beginning of the Sequence.

- The beginning of the designated Sequence Step.

- The beginning of the designated Sequence Step and on each loop of the Sequence Step.

- The beginning of the designated Sequence Step but only on the designated Loop Count

The start trigger can be offset from 0-2M words. The width of the SYNC pulse can be from 1 to 4097 words.

During the period of the sync pulse, the data being presently output can be replaced by other data from the waveform memory.

A sequence can run continuous or for a burst from 1 to 1M times.

#### 3.1.2.7 14 - Bit D/A

The gain reference level and buffered AM modulation inputs are SUMed, analog wise, and applied to this D/A as a reference input.

Note 1: The DAC output is not perfectly proportional to the reference input. Low gains may not be accurate and deep modulations will not be symmetrical.

Note 2: The bandwidth of the reference input is limited. Thus AM modulation is limited to ~100kHz for small modulations and perhaps down to 20kHz at 80% modulation.

#### 3.1.2.8 Filter

The filter is a 7-pole elliptic filter with a frequency cutoff of 50 MHz. It is designed to improve the shape of sine waves above 10MHz. It will attenuate the amplitude of sine wave outputs ~10% at 10MHz and up to 25% at 25MHz.

#### 3.1.2.9 Relay

The arbitrary waveform output can be relay isolated from the front panel.

#### 3.1.2.10 SIGOUT1/SIGOUT2 Outputs

The MA1801A signals, SIGOUT1 and SIGOUT2, can be programmed to output one of a number of signals for monitoring MA1801A status or triggering other devices. SIGOUT1 and SIGOUT2 for both channels are enabled together.

#### 3.2 Module Connectors

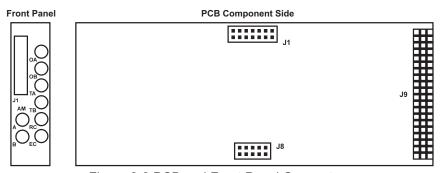

Figure 3-3 illustrate the MA1801A PCB and front panel connectors.

Figure 3-3 PCB and Front Panel Connectors

#### 3.2.1 M/MA-Module Logic Bus Connector (PCB-J9)

The M/MA-Module logic bus connector contains signal and voltage connections for the M/MA-Module interface logic.

#### 3.2.2 Inter Module Connector (PCB-J8)

The inter module connector is used to link adjacent MA1801A modules in a master slave mode.

#### 3.2.3 FPGA Program Connector (PCB-J1)

The FPGA program connector is used to program the MA1801A FPGA serial PROM.

#### 3.2.4 Coaxial Connectors (Front Panel MCX)

The front panel coax connectors provides various analog input and output signals. (See appendix B for pin assignments).

OA: Channel A waveform output.

OB: Channel B waveform output.

TA: Channel A trigger 1 input (TRIG1A).

TB: Channel B trigger 1 input (TRIG1B).

RC: Channel A & B shared reference clock input.

EC: Channel A & B shared external clock input.

AM A: Channel A amplitude modulation input.

AM B Channel B amplitude modulation input.

#### 3.2.5 I/O Connector (Front Panel J1)

The front panel I/O connector provides various digital input and output signals. (See appendix B for pin assignments).

- A: Channel A trigger 2 input (TRIG2A).

- B: Channel B trigger 2 input (TRIG2B).

- E: Channel A signal output 1 (SIGOUT1A).

- F: Channel A signal output 2 (SIGOUT2A).

- H: Channel B signal output 1 (SIGOUT1B).

- J: Channel B signal output 2 (SIGOUT2B).

- C,D,K: Signal ground.

# 3.3 Identification/Configuration Registers

#### 3.3.1 M-Module PROM Registers

The MA1801A supports the identification function called IDENT. This IDENT function provides information about the module and is stored in sixteen word deep (32 byte) serial EEPROM. Access is accomplished with read/write operations on the last address in I/O space and the data is read one bit at a time.

The MA1801A also supports the VXI-IDENT function introduced by Hewlett-Packard. This function is not part of the approved ANSI/VITA 12-1996 standard. This extension to the M-module IDENT function increases the size of the EEPROM to at least 64 words (128 bytes) and includes VXI compatible ID and Device Type Registers. Details are shown in table 3-1

| Word  | Description            | Value (hex) |

|-------|------------------------|-------------|

| 0     | Sync Code              | 5346        |

| 1     | Module Number          | 00CC        |

| 2     | Revision Number        | 0001        |

| 3     | Module Characteristics | 9E37        |

| 4-7   | Reserved               | 0000        |

| 8-15  | M-Module Specific      | 0000        |

| 16    | VXI Sync Code          | ACBA        |

| 17    | VXI ID                 | CF0F        |

| 18    | VXI Device Type        | 4709        |

| 19-31 | Reserved               | 0000        |

| 32-63 | M-Module Specific      | 0000        |

Table 3-1 M/MA Module EEPROM IDENT Words

#### Notes:

- 1) The Revision Number is the functional revision level of the module. It does not correspond to the hardware assembly level.

- 2) The Module Characteristics bit definitions are:

| Bit(s) | Description                          |

|--------|--------------------------------------|

| 15     | 1 = burst access                     |

| 14/13  | 00 (unused)                          |

| 12     | 1 = needs ±12V                       |

| 11     | 1 = needs +5V                        |

| 10     | 1 = trigger outputs                  |

| 9      | 1 = trigger inputs                   |

| 8/7    | 00 = no DMA requestor                |

| 6/5    | 01 = interrupt type A (software EOI) |

| 4/3    | 10 = 32-bit data                     |

| 2/1    | 11 = 24-bit address                  |

| 0      | 1 = memory access                    |

3) The VXI Device Type word contains the following information:

Bit(s) Description

15-12 4 = 524288 bytes of required memory

11-0 709<sub>16</sub> = Talon specified model code

# 3.3.2 IO Registers

There are a variety of registers used to configure and control the MA1801A module. The registers are addressable within the I/O Space. An address map and details of the registers is provided in Appendix A.

# 4 Register Operation

The MA1801A register operation involves programming several control registers as well as the waveform memory. The entire MA1801A memory map is listed in appendix A.

The following sections describe typical arbitrary waveform generator functions and the register programming required for the MA1801A. Example code is listed in appendix C.

Two register access functions are used to read and write data from/to the MA180. These functions, peek16 and poke16, would be replaced by the users I/O library calls that will perform the similar function. The functions are described below:

Peek16: Reads 16 bits of data from the specified address.

Peek16 (int address, unsigned short \*data)

Poke16: Writes 16 bits of data to the specified address.

Poke16 (int address, unsigned short data)

### 4.1 Initialize Clock/DAC Registers

The MA1801A clock and DAC registers must be initialized before values are written to them.

```

#define CLKGEN

0 \times 40

#define GAIN_A

#define GAIN_B

0 x82

0 \times 86

#define OFFSET A

0 x8A

#define OFFSET_B

#define TRIG1AREF

0 x8 E

0 x9 2

#define TRIG1BREF

0 \times 96

#define RCLKREF

#define ECLKREF

0 v 9 A

0x9E/*

This function initializes the clock generator and DAC register sequence bits of the MA1801A module.

Input:

None

Return Value:

int initModule(void)

/* initialize clock generator sequence bits */

Poke16(CLKGEN, 0x0F00);

Poke16(CLKGEN + 2, 0xB0F0);

Poke16(CLKGEN + 4, 0x0000);

Poke16 (CLKGEN + 6, 0x03E8);

Poke16 (CLKGEN + 8, 0x0700);

Poke16 (CLKGEN + 10, 0x2494);

/* initialize channel A gain DAC rigister bits */

Poke16(GAIN_A, 0x08C8);

/* initialize channel A gain DAC rigister bits */

Poke16(GAIN_B, 0x48C8);

/* initialize channel A offset DAC rigister bits */Poke16(OFFSET_A, 0x87FF);

/* initialize channel B offset DAC rigister bits */Poke16(OFFSET_B, 0xC7FF);

/* initialize TRIG1A DAC rigister bits */

Poke16(TRIG1AREF, 0x0940);

/* initialize TRIG1B DAC rigister bits */

Poke16(TRIG1BREF, 0x4940);

/* initialize REFCLK DAC rigister bits */

Poke16(RCLKREF, 0x8940);

/* initialize EXTCLK DAC rigister bits */

Poke16(ECLKREF, 0xC940);

return 0:

```

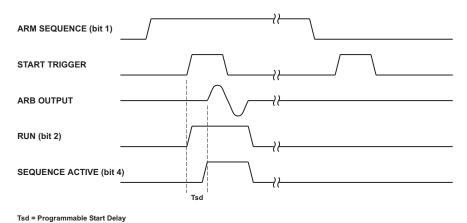

#### 4.2 Check the MA1801A Arm Status

Before programming the MA1801A, the channel should be disarmed to prevent the start trigger from generating an output before the new settings are written. Checking the MA1801A arm status is performed by reading the "Run Control Register", section 2.1 of Appendix A. The run control register contains the arm and execution status for both channels.

The following timing diagram illustrates the arm and execution status bits for the triggered mode receiving a start trigger while armed and not armed.

Figure 4-1 Status Bit Timing

The following code example returns the arm bit for the specified channel,

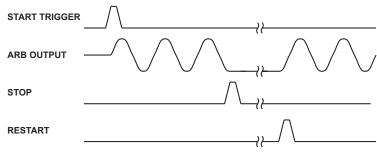

# 4.3 Stopping a Channel

There are three ways to stop a MA1801A channel from outputting;

- 1. Set the arm bit low in the run control register.

- 2. Set the reset sequence bit high in the run control register.

- 3. Isolate the output

Setting the arm bit low prevents the MA1801A from responding to the start trigger. Once the current waveform segment has completed the output will remain at the level of the last sample point.

Setting the reset sequence bit high forces the arm, run and sequence active bits low. The output will go to the programmed offset value.

The following code example will disarm or reset the specified channel based on the user selection,

```

int stopChannel(short channel, short type)

unsigned short runctrl, startctrl;

/* read run control register */

Peek16(RUNCTRL, &runctrl);

/* set the arm bit low if type == DISARM */

if (type == DISARM)

/* only disarm the specified channel */

if (channel == CHANNEL A)

/* mask off channel A arm bit */

runctrl &= 0xFFFE;

else

/* mask off channel B arm bit */

runctrl &= 0xFEFF;

else if (type == RESET || type == ISOLATE)

if (type == reser | | -2:5 |

if (type == ISOLATE) {

/* read start control register */

Peek16(STARTCTRL, &startctrl);

isolate the output before resetting */

if (channel == CHANNEL A)

/* isolate channel A */

startctrl &= 0xFF3F;

/* isolate channel B */

startctrl &= 0x3FFF;

/* write start control register */

Poke16(STARTCTRL, startctrl);

}

/* only reset the specified channel */

if (channel == CHANNEL A)

/* set channel A reset bit */

runctrl |= 0x8;

/* set channel B reset bit */

runctrl |= 0x800;

/* program the control register */

Poke16(RUNCTRL, runctrl);

return 0;

```

# 4.4 Setting the Amplitude/Offset

Output amplitude for each of the channels may be programmed separately within the range of 20 mV to 20 Vp-p into an open circuit, and 10 mV to 10 Vpp into  $50\Omega$ .

Offset for each of the channels may be programmed separately within the range of  $\pm 10V$  into an open circuit and  $\pm 5V$  into  $50\Omega$ .

Note that output peak voltage may never exceed  $\pm 10V$  into an open circuit and  $\pm 5V$  into  $50\Omega$ . Amplitude and offset may be set freely within a 10V window, as long as the following limits are kept:

```

| offset | + Amplitude \div 2 \le 10

```

The amplitude of each output channel is programmed by setting the gain reference of the 14 bit DAC. The gain reference can be programmed from 0.01V to 10V with a resolution of 0.005V. The DAC output is not perfectly proportional to the reference input. Low gains may not be accurate and is therefore recommended that the gain reference be programmed greater than 1. Low amplitude waveforms can be achieved even with a gain greater than 1 by programming the sample memory to limit the output voltage. An external attenuator may also be used to generate low amplitude waveforms.

The following code example will program the gain and offset references,

```

int gainAddr = GAIN A, offsetAddr = OFFSET A; unsigned short gain\overline{D}ata = 0, offsetData = \overline{0}, runCtrl;

/* update the addresses if channel B */

if (channel == CHANNEL_B) {

gainAddr += 4;

gainData = 0x4000;

offsetAddr += 4

offsetData = 0x4000;

/* calculate gain data */

gainData += (gain * 200) + 2048;

/* calculate offset data */

offsetData += 0x8000 + (offset * 400) + 2048;

/* program the gain register */

Poke16 (gainAddr, gainData);

/* program the offset register */

Poke16(offsetAddr, offsetData);

/* update the reference DACs */

/* read run control register */

Peek16(RUNCTRL, &runCtrl);

/* preserve arm bits and set the D/A update bit */

runCtrl = (runCtrl & 0x101) | 0x8000;

/* program the run control register */

Poke16(RUNCTRL, runCtrl);

query until D/A update complete */

/* read run control register */

Peek16(RUNCTRL, &runCtrl);

} while ((runCtrl & 0x8000) == 0x8000);

return 0;

```

# 4.5 Setting the Sample Clock

Data is clocked to the digital to analog converter (DAC) which, in turn, generates the waveform shape that was downloaded to the arbitrary waveform memory.

Users should be careful not to confuse waveform frequency with sample clock frequency. The sample clock frequency defines the frequency at which the generator clocks data points. The frequency of a given waveform is computed using the sample clock frequency and the number of data points. Use the following equation for computing the frequency of (one cycle of) a waveform:

Waveform Frequency = Sample Clock ÷ Number of data points

For example, using a sample clock of 100MHz with a 2000-point waveform will generate a 50kHz waveform at the output connector.

The sample clock can be set to the internal clock generator, or the external front panel input.

The following code example will program the sample clock source and frequency,

```

#define CLKCTRL

#define CLKGEN

0 \times 40

This function programs the sample clock source and frequency of the specified MA1801A channel.

channel: (0 = channel A, 1 = channel B)

source: (0 = internal, 1 = external)

source:

freqHz:

(10 to 125,000,000)

Return Value:

int setSampleClock(short channel, short source, double freqHz, short refSource)

int div1, div2, fbdiv, cgdata;

unsigned short data, clkctrl; double cgfreq;

short coarseTune = 7;

time t t1, t2;

/* read clock control register */

Peek16(CLKCTRL, &clkctrl);

set the sample clock source */

if (channel == CHANNEL A) {

/* set new value *7

clkctrl = (clkctrl & 0xFCFF) + (source << 8);

```

4-4

```

} else {

/* set new value */

clkctrl = (clkctrl & 0xF3FF) + (source << 10);</pre>

/* set internal clock generator */

if (freqHz == 0.0 || source == EXTERNAL) {

/* get LSW of clock generator register 2 */

Peek16(CLKGEN + 6, &data);

/* disable the generator */

data |= 0x2000;

/* set LSW of clock generator register 2 */ Poke16(CLKGEN + 6, data);

} else {

/* claculate the control register divide count */

for (cgfreq = freqHz, div2 = 0; cgfreq < 20000000.0; div2++)

cgfreq *= 10;</pre>

blutv - cgireq < 10000000.00) {

div1 = 0xA; /* 20 */

fbdiv = cgfreq < 2000000.00) {

div1 = 0x9; /* 10 */

fbdiv = cgfreq < 2000000.00) {

div1 = 0x9; /* 10 */

fbdiv = cgfreq < 0.0005;</pre>

} else if (cgfreq < 100000000.00) {

div1 = 0x1;      /* 2 */

fbdiv = cgfreq * .0001;</pre>

} else {

div1 = 0;

div1 = 0; /* 1 */

fbdiv = cgfreq * .00005;

/* program new post divide value and reference enable */

if (channel == CHANNEL A)

clkctrl = (clkctrl & 0xfff0) + div2;

clkctrl = (clkctrl & 0xff0f) + (div2 << 4);

/* calculate clock generator register 2 */ cgdata = ((fbdiv & 0xFF) << 24) + (div1 << 16) + (refSource << 12) + 0x3E8;

/* write clock generator register 2 LSW */

Poke16 (CLKGEN + 6, cgdata & 0xFFFF);

/* write clock generator register 2 MSW */ Poke16 (CLKGEN + 4, cgdata >> 16);

/* calculate clock generator register 3 */

cgdata = (coarseTune << 24) + (fbdiv >> 8) + (refSource * (7 << 17)) + 0x2480;</pre>

/* write clock generator register 3 LSW */Poke16 (CLKGEN + 10, cgdata & 0xFFFF);

/* write clock generator register 3 MSW */ Poke16 (CLKGEN + 8, cgdata >> 16);

}

/* get LSW of clock generator register 1 */

Peek16(CLKGEN + 2, &data);

/* select the generator */

if (channel == CHANNEL_A)

data &= 0xF7FF;

data |= 0x800;

/* set LSW of clock generator register 1 */ Poke16(CLKGEN + 2, data);

/* write out clock control register */

Poke16(CLKCTRL, clkctrl + 0x1000);

/* read clock control register and check bit 12 */

Peek16 (CLKCTRL, &clkctrl);

} while (clkctrl & 0x1000);

/* delay for clock generator to settle */

t1 = clock();

do {

t2 = clock();

} while ((t2 - t1) < 3);

```

```

return 0;

```

# 4.6 Programming the Waveform Memory

The MA1801A generates arbitrary waveforms with 14 bits of vertical resolution. Any waveform it generates must first be downloaded to waveform memory.

The waveform memory is configured in two banks of 32-bit words. Each word represents two points on the horizontal (or time) waveform scale. Each word has a horizontal address that can range from 0 to 262142 (primary bank) or 262144 to 524284 (secondary bank) and a vertical address (or voltage level) that can range from 0 to 16383 (14 bits) stored in the upper and lower 16 (lower 16 bits is the first point). Using a high speed clocking circuit, the digital contents of the arbitrary waveform memory are extracted and routed to the Digital to Analog Converter (DAC). The DAC converts the digital data to an analog signal, and the output amplifier completes the task by amplifying or attenuating the signal at the output connector.

There is no need to use the complete memory bank every time a waveform is generated. The Waveform memory can be divided into smaller segments and different waveforms can be loaded into each segment. The various segments may then be loaded into a sequence table to generate long and complex waveforms. The sequence table can link up to 512 segments, while each segment can loop up to 65535 times. Note that sequence generators are separate for each channel. The separation exists also in master-slave mode.

The following code example will program the specified waveform memory with the contents of the data array.

```

#define MEMORY

0 \times 2

#define EMADDR

#define EMDATA

0 xC0

This function programs the waveform memory of the specified MA1801A channel.

Imput:

channel: (0 = channel A, 1 = channel B)

memory: (0 = primary, 1 = secondary)

offset: (0 - 0x3FFFF)

Return Value:

int setWavformMemory(short channel, short memory, int offset, int samples, unsigned short data[])

unsigned short membsy, memgrnt, memreg;

unsigned short emaddr, *emdata;

int error = 0;

while (0x1) {

/* read the memory register */

Peek16(MEMORY, &memreg);

/* update the memory variable to include the channel */

memory += (channel * 2);

/* check the grant bit to see if we have to request memory */

memgrnt = 1 << (4 + memory);

if ((memgrnt & memreg) == 0) {

/* check the busy bit befor requesting memory */

membsy = memgrnt << 4;</pre>

if ((membsy & memreg)) {

error = ERROR MEMREQ;

break;

/* request and select memory */

memreg = (memory << 12) + (1 << memory);

Poke16 (MEMORY, memreg);

/* read the memory register */

Peek16 (MEMORY, &memreg);

/* did we get memory ? */

if ((memgrnt & memreg) == 0) {

error = ERROR_MEMREQ;

}

1

/* write the extended memory address and page MSW */

emaddr = (offset >> 16);

Poke16(EMADDR, emaddr);

/* write the extended memory address and page LSW */

emaddr = offset;

```

4-6

# 4.7 Programming the Sequence Memory

The sequence generator is a very powerful tool that links waveform segments. The sequence logic is useful for generating long waveforms with looped sections. The looped waveform only has to be programmed once and the sequence logic will loop on this segment as many times as selected. When in sequenced mode, there is no loss of time between linked or looped segments. Each channel has its own dedicated sequence generator, even in master-slave mode. Sequence memory must be loaded to the generator before sequenced waveforms can be generated. The sequence memory contains 512 steps where each step specifies the following:

- Waveform address This specifies the address in the waveform memory that will be output for specified step.

- Number of points This specifies the number of points to output for this step.

- Loop Count This specifies the loop count for this step.

- Mode This specifies the way the instrument advances from the current step to the next step. Three modes are available:

STEP The sequence is advanced to the next step only when a valid trigger is received. The output of the MA1801A generates the current segment continuously until a trigger signal advances the sequence to the next step. If loops were specified, they are ignored in STEP mode.

SING The MA1801A idles between steps until a valid trigger signal is sensed. After outputting the specified number of loops, the output level idles at a DC level equal to the last point of the waveform. The sequencer will step to the next step in the sequence when it receives its next valid trigger.

SING1 The MA1801A idles between steps until a valid trigger signal is sensed. After a trigger, the generator outputs one waveform loop. Then, the output level idles at a DC level equal to the last point of the last generated waveform. If loops were programmed, the sequencer repeats this segment each time a trigger is received, until the number of loops specified for this step has been reached. After reaching this number, the sequencer advances to the next step in the sequence.

• Source - This specifies the advance trigger signal listed below:

Signal1 low

Signal1 high

Signal1 falling

Signal1 rising

Signal2 low

Signal2 high

Signal2 falling

Signal2 rising

Primary not granted

Secondary not granted

Auto advance

Jump Source - This specifies the jump trigger signal. When the advance trigger

occurs and the jump trigger is true, the next sequence step will be set to the "Jump

Sequence" instead of the next sequential step. One of the features of the MA1801A

sequencer is the ability to specify a jump source. This feature allows the user to

perform "ping-pong" operation outputting data from one memory bank while updating the other. The jump source signal selections are listed below:

```

Signal1 low

Signal1 high

Signal1 falling

Signal2 rising

Signal2 high

Signal2 falling

Signal2 rising

Primary granted

Primary not granted

Secondary granted

Secondary not granted

Timeout

Auto Jump

```

- Jump Sequence This specifies the step number to jump to when the jump source is true.

- Flags There are five sequence flags described below:

SeqFlag1 (Sequence Flag One) This flag can be set high or low and routed to the front panel SigOut signals and/or the backplane TRIGA/TRIGB signals.

SeqFlag2 (Sequence Flag Two) Sequence flag 2 can be set high or low and routed to the front panel SigOut signals and/or the backplane TRIGA/TRIGB signals.

SeqStop (Sequence Stop) This flag indicates that the current step is the last step (1 - Stop after this step).

JumpRet (Jump Return) This flag forces a jump step to return after the jump step is complete.

JumpImm (Jump Immediate) This flag tells the sequencer to jump when the jump trigger is true even if there are loops remaining (1 - Jump immediately)

Each sequencer has two signals that are used for advancing and jumping. The sequence signals can be selected from a number of sources listed below:

1. Front Panel

TRIG1A

TRIG2A

TRIG1B

TRIG2B

2. M-Module Backplane

**TRIGA**

**TRIGB**

3. MA1801A Internal

**TIMERA**

**TIMERB**

MARKER1A

MARKER2A

MARKER1B

MARKER2B

The following code example will program the sequencer signals of the specified channel.

```

This function programs the sequence source signals of the specified MA1801A channel.

Input:

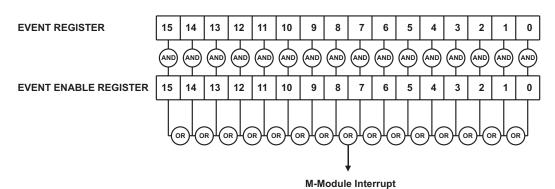

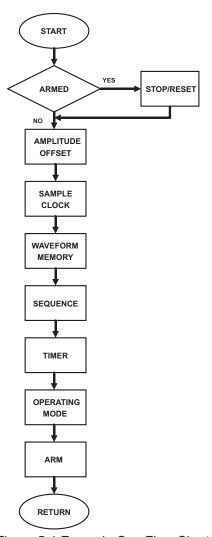

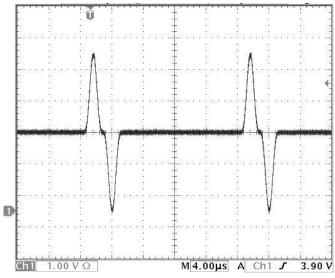

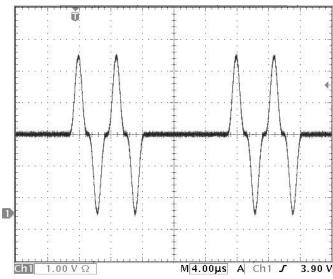

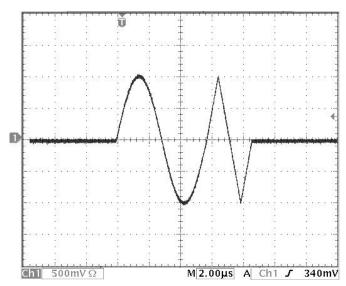

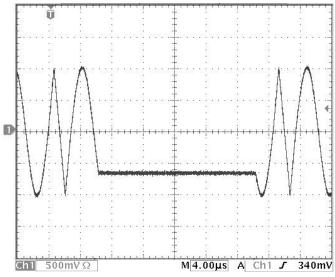

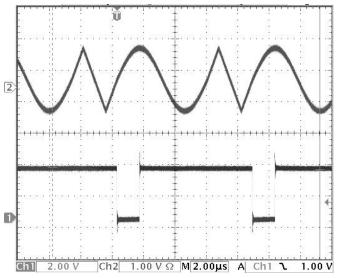

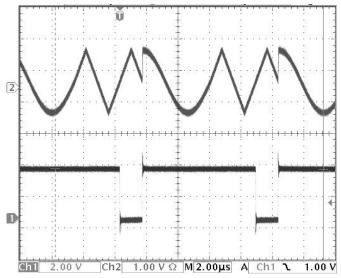

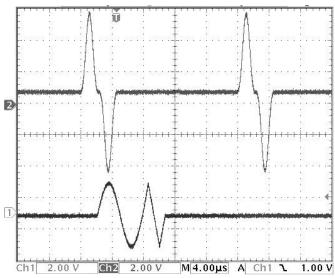

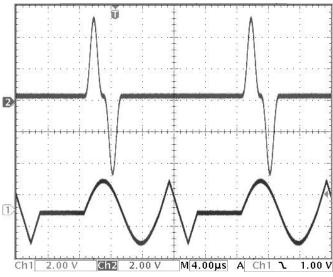

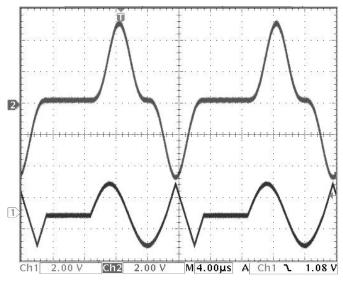

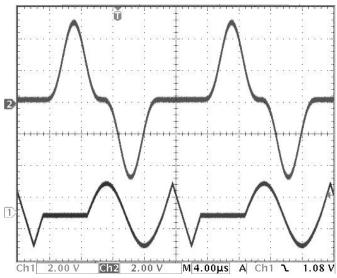

channel (0 = channel A, 1 = channel B)